# ISO 9001:2008 Certified

International Journal of Engineering and Innovative Technology (IJEIT) Volume 5, Issue 11, May 2016

# Design rules of the CMOS inverter for voltage converters

Jan Marek, Jiří Hospodka, Ondřej Šubrt Faculty of Electrical Engineering at Czech Technical University in Prague, Technická 2, 166 27 Prague, Czech Republic

Abstract—This paper presents a description of the dominantcharacteristics of the CMOS inverter, which is used for voltage converters-charge pumps applications. This circuit controls transport charge between main capacitors to create a higher DC voltage. The significant part of the pump losses is caused by the inverter cross current. This current flows through the inverter in transition state and discharges the capacitor, therefore decreases the pump voltage gain. The CMOS inverter design is based on the analog block description for high-voltage integrated circuits using BSIM model equations. The main benefit of this article is derivated analytical relationship between width and length of the NMOS and PMOS transistors to achieve the static power minimization. The derivation has been performed based on the sensitivity analysis. The design relationship are applicable to the other MOSFET models, as EKV. The characteristic of the proposed circuit has been verified by simulation in ELDO Spice. Analysis results show that the cross current is reduced by ten times in comparison with the value of the standard digital inverter (with symmetrical voltage transfer characteristics). This improvement was achieved while keeping relatively large area of both transistors satisfying the dynamic properties.

*Index Terms*—CMOS inverter, cross current, charge pump,BSIM model, high-voltage, sensitivity.

#### I. INTRODUCTION

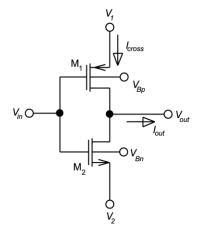

A CMOS inverter is a basic block (Fig. 1) for digitaldesign circuits which performs a logic operation from A to A. However, there are also aplications in the analog domain; bothcontinuous-time circuits (oscillators, amplifiers) and discrete-time analog circuits (voltage convertors). Although discrete-timeanalog circuits seem to be digital circuits from a system perspective, the internal state of the system is time continuousduring each period of the clock signal. Charge pumps ([6], [7],[8]) are a typical group of switched-capacitor (SC) circuits, where the inverter drives switch to a transport charge between the main capacitors. The output voltage of the inverter with acapacitive load may be in an undefined state from the view of logic levels because energy accumulated in capacitors must be a continuous function of time. Results of the transientanalysis show that the dominant part of losses in chargepumps is caused by a DC cross current that flows throughan inverter operating in the linear region of voltage transfercharacteristics. This is undesirable because the cross current greatly decreases a pump's voltage gain while losses causedby propagation delays of the inverter are very small.

Current research deals with the dynamic behavior of theinvertor and transistor sizing, which is based on the equivalent digital model. A number of detailed analyses in digital circuits([1], [4], [12]–[19]) have been reported ([15]–[19]). The inverteroperating in a strong inversion is known. The width of the PMOS must be 2-3 times width of the NMOS [1] (symmetricaltransfer characteristics). However, this setting may not suit inanalog circuits.

In the article, the inverter design for voltage converters is discussed in order to minimize the average cross current duringthe period of the clock signal. Using BSIM model equations, an analytical description of DC characteristics ([1], [4]) willbe found for this purpose. The strong inversion region isexpected in the high-voltage circuits, where the behavior ofthe MOSFET models for analog structured design is correct. Consequently, it is not necessary to admit a specified technology, because the EKV parameters are extracted from thecurves simulated using the BSIM models [3]. The main benefitof this article is an *analytical relationship* between sizing(width and length) of both the transistors to achieve the staticpower minimization of the charge pump inverter. The acquiredestimation can be used as the baseline for the optimizing algorithm.

# II. BSIM MODEL EQUATION

A real model of the MOSFET, like BSIM involves manyeffects [2]. It contains many model parameters and any derivation is very difficult (implicit form, solving of irrational equations, etc.). So, the equations are simplified to only describe the dominant characteristics for the design purpose. The static model of MOSFET is discussed as introduced in the previous text.

For MOSFET operation in high-voltage circuits where  $V_{GS} \ll V_{TH}$ , the following conditions must be true:

- long channel MOSFET

- strong inversion region.

Channel length is an important parameter because of the breakdown voltage. The electrical field in a structure induced by an applied voltage must be significantly less than the critical electrical field,  $E = \frac{v}{L_{eff}} \le E_{crit}$ , where  $L_{eff}$  is effective channel length. A critical electrical field is limited to the value given by a semi-empiric model [2].

The effective channel length is relative to the applied voltage *Vmax* (gate-source, drain-source) defined as

$$L_{eff} \gg V_{max} \frac{\mu_{eff}}{2v_{sat}},\tag{1}$$

where  $v_{sat}$  is the saturation velocity (model parameter) and  $\mu_{eff}$  is effective mobility.

# ISO 9001:2008 Certified

# International Journal of Engineering and Innovative Technology (IJEIT) Volume 5, Issue 11, May 2016

A drain current model is given by a single equation [2]. The transition from triode to the saturation region is ensured through an effective drain-source voltage.

$$V_{DSeff} = \begin{cases} V_{DS}, & \text{for triode region} \\ V_{DSsat}, & \text{for saturation region} \end{cases}$$

(2)

and for long channel MOSFETs, the saturation drain current  $V_{DS} = V_{DSsat}$  is given by:

$$(3) I_{Dsat0} = \frac{1}{2} \frac{W}{L} c_{oxe} \mu_{eff} V_{DSsat} (V_{GS} - V_{TH}),$$

where  $c_{oxe}$  is the electrical oxide capacitance. The boundary between the triode and saturation regions is predicted by the voltage ( $V_{GS^-}$   $V_{TH}$ ) and applies a bias voltage effect and further model parameters (channel length and width...) included in the bulk-charge equation [2], labeled  $A_{bulk}$ .  $A_{bulk}$  is closed to unity for relatively high source-bulk bias voltage. In the other words

$$V_{DSsat} = \frac{V_{GS} - V_{TH}}{A_{bulk}} \approx V_{GS} - V_{TH} \text{ for } V_{SB} > V_{GS}.$$

(4)

Generally, the output I-V curve in the saturation  $region(V_{DS} > V_{DSsat})$  is written by several physical mechanisms. Nevertheless, considering the condition (1) short channel effect- channel length modulation (CLM) and Substrate CurrentInduced Body Effect (SCBE) can be neglected. Then the draincurrent increases linearly with the  $V_{DS}$  voltage. The slope ofthe output characteristics is mainly determined by Early voltage  $V_{ADIBL}$  due to the drain-induced barrier lowering (DIBL)effect ([1], [2], [5]).  $V_{ADIBL}$  is directly proportional to thevoltage  $V_{GS}$ , as is shown bellow. Moreover, the equation (5) contains the model parameters PDIBLC2 and PDIBLCB [2].

$$V_{ADIBL} = \frac{1}{2} \frac{V_{GS} - V_{TH}}{\text{PDIBLC2} (1 - \text{PDIBLCB} V_{SB})}$$

(5)

The complex drain current equation may be expressed by the formula

$$I_{Dsat} = I_{Dsat0} \left( 1 + \frac{V_{DS} - V_{DSsat}}{V_{ADIBL}} \right)$$

for  $V_{DS} \ge V_{DSsat}$ .

The drain current in the triode region is a function of the  $V_{DS}$  voltage ( $V_{GS} = \text{const.}$ ). The maximum of the parabolic function  $I_{DS0} = f(V_{DS})$  corresponds to the voltage  $V_{DSsat}$  because of the neglected CLM mechanism ([1], [2], [5]). Then, the relationship between the drain-source voltage  $V_{DS}$  and the saturation drain current  $I_{Dsat0}$  [5] can be written simply as

$$I_{DS0}\left(V_{DS}\right) = -\frac{I_{Dsat0}}{V_{DSsat}^2}V_{DS}^2 + \frac{I_{Dsat0}}{V_{DSsat}}2V_{DS}$$

for  $V_{DS} < V_{DSsat}$ .

Fig. 1. The CMOS inverter.

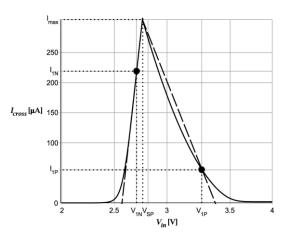

Fig. 2. DC current characteristics of the inverter.

# III. STATIC PARAMETERS OF THE CMOS INVERTER

A diagram of the CMOS inverter schematic is shown in Fig. 1. All voltages are referenced to the *ground* and  $V_1 - V_2 > V_{THN} + |V_{THP}|$ .

The inverter's cross current characteristics is shown in Fig. 2. A general form of the analytical expression of the cross current is divided into the three cases:

$$I_{cross} = \begin{cases} I_{DsatN} | V_{GS} = V_{in} - V_2, & \text{for C1} \\ I_{DsatP} | V_{SG} = V_1 - V_{in}, & \text{for C2} \\ 0, & \text{otherwise,} \end{cases}$$

(8)

where condition C1 is:  $V_2 + V_{THN} \le V_{in} \le V_{SP}$  and C2 is:  $V_{SP} \le V_{in} \le V_I - |V_{THP}|$ .

Cross current is maximal at the switching point  $V_{in} = V_{SP}$ , see [1]. Both transistors  $M_1$  and  $M_2$  are in the saturation region (Eq. 6) for this case and the drain current of each MOSFET must be equal:

$$I_{DsatN}|_{V_{GS}=V_{SP}-V_2} = I_{DsatP}|_{V_{SG}=V_1-V_{SP}},$$

(9)

if the output current (see Fig. 1) is zero ( $I_{out} = 0$ ). Equation(9) is more than third order for variable  $V_{SP}$ , thus simplifying preconditions will be introduced.

#### ISO 9001:2008 Certified

# International Journal of Engineering and Innovative Technology (IJEIT) Volume 5, Issue 11, May 2016

Firstly, Early voltage (Eq. 5) limits to infinity, wherefromit is compared  $I_{Dsat0N} \approx I_{Dsat0P}$ . Secondly, the absolutely value of the drain currents of the PMOS and NMOS transistors for the derivation  $V_{SP}$  are not important; only transconductance is important. The slope of the cross current characteristics on each interval is mainly given by the linear part of the voltage  $V_{GS^-}$   $V_{TH}(V_{SB})$  (MOS transconductance in strong inversion is a linear function of the gate-source voltage), while other powers at that voltage are not taken into account. Hence, the bulk charge equation [2] is adjusted to

$$A_{bulk0}(V_{SB}) = A_{bulk}|_{(V_{GS}-V_{TH})_{eff}=0}$$

and with the effective mobility substituted into the equation(3) at zero bias voltages. Finally, the formula of the switchingpoint for the BSIM model [1] can be expressed in the modifiedform:

$$V_{SP} = \frac{V_1 - |V_{THP}(V_{BS})| + \sqrt{R_{\overline{b}}^{\underline{a}}}[V_2 + V_{THN}(V_{SB})]}{1 + \sqrt{R_{\overline{b}}^{\underline{a}}}}, \quad (10)$$

where

$$a=\frac{c_{oxeN}\mu_{effN}|_{V_{GS}=V_{SB}=0}}{A_{bulk0N}|_{V_{SB}=0}},\,b=\frac{c_{oxeP}\mu_{effP}|_{V_{SG}=V_{BS}=0}}{A_{bulk0P}|_{V_{BS}=0}}$$

and  $R=\frac{W_n}{L_n}\frac{L_p}{W_p}$ .

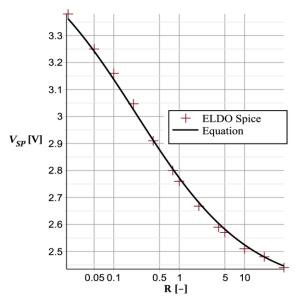

The switching point is an important parameter for the calculation of DC power because of the discontinuous cross current characteristics at that point, as it is shown in Fig. 2. The typical characteristics of the dependence of the switching point on the ratio dimensions of bothtransistors is shown in Fig. 3.

Fig. 3. Switching point analysis – dependence on the ratio R

Static power during the inverter's output voltage crossing between logic 1 and logic 0 is defined as

$$P_{DC} = \int_{V_{2}}^{V_{1}} I_{cross} (V_{in}) dV_{in} = \int_{V_{2}+V_{THN}}^{V_{SP}} I_{DsatN} (V_{in}) dV_{in} + \int_{V_{1}-|V_{THP}|}^{V_{1}-|V_{THP}|} + \int_{V_{SP}}^{I} I_{DsatP} (V_{in}) dV_{in}.$$

(11)

The solution of equation (11) exists, but it is confusing and unnecessary for the estimation of the power dissipation. Results of the numeric integration of equation (11) shows that function is primarily determinend by the function  $\arctan^1$ , that can be approximated by its argument (linear function) at  $\operatorname{zerolim}_{x\to 0}\left(\frac{\arctan(x)}{x}\right)=0$ . A simpler approach is based on an approximation of the characteristics (Fig. 1) in intervals  $V_{in} \in \langle V_2 + V_{THN}, V_{SP} \rangle$  and  $V_{in} \in \langle V_{SP}, V_1 + |V_{THP}| \rangle$  by linear interpolation for two points at each interval:

At the point coressponding to the known voltage V<sub>SP</sub>that is substituted into equation (5):

$$I_{max}|_{V_{in}=V_{SP}} = I_{DsatN}|_{V_{GS}=V_{SP}-V_2} \simeq$$

$\simeq I_{DsatP}|_{V_{SG}=V_1-V_{SP}}$

At the point where  $|V_{GS}|$  is greater than the thresholdvoltage  $|V_{TH}|$  (strong inversion region), the transistoris operating at the edge of the saturation  $\operatorname{region}(M_I)$  for  $V_{in} \in \langle V_{SP}, V_1 + |V_{THP}| \rangle$  and  $M_2$  for  $V_{in} \in \langle V_2 + V_{THN}, V_{SP} \rangle$ ), where the drain current is approximately the linear function of the gate-source voltage. Itmeans that quadratic part of  $V_{GS}$  voltage from expression $(V_{GS}-V_{TH})^2$  must be less than its linear part. Assuming the equality of these parts, two solutions exists. The first one is  $V_{GS}=0$  that is ignored and the second is  $V_{GS}=2|V_{TH}|^2$ :

$$I_{1} = \begin{cases} I_{1N} = I_{Dsat0N}|_{V_{GS} = V_{1N} = 2V_{THN}}, \text{ for NMOS} \\ I_{1P} = I_{Dsat0P}|_{V_{SG} = V_{1P} = 2|V_{THP}|}, \text{ for PMOS} \end{cases}$$

thence, new formula for cross current characteristics can be expressed as

$$\tilde{I}_{cross} \approx \begin{cases} I_{1N} \frac{V_{SP} - V_{in}}{V_{SP} - V_{2} - 2V_{THN}} + I_{max} \frac{V_{2} + 2V_{THN} - V_{in}}{V_{2} + 2V_{THN} - V_{SP}}, & \text{for C1} \\ I_{1P} \frac{V_{SP} - V_{in}}{V_{SP} - V_{1} + 2|V_{THP}|} + I_{max} \frac{V_{1} - 2|V_{THP}| - V_{SP}}{V_{1} - 2|V_{THP}| - V_{SP}}, & \text{for C2} \\ 0, & \text{otherwise,} \end{cases}$$

where condition C1 is:  $V_2 + V_{THN} \le V_{in} \le V_{SP}$  and C2is:  $V_{SP} < V_{in} \le V_I - |V_{THP}|$ . The equation (12) allows to calculate the static power as the triangle area:

$$\tilde{P}_{DC} \approx \frac{1}{2} I_{max} \left( \frac{I_{max}(V_1 - 2|V_{THP}|) - I_{1P}V_{SP}}{I_{max} - I_{1P}} - \frac{I_{max}(V_2 + 2V_{THN}) - I_{1N}V_{SP}}{I_{max} - I_{1N}} \right). \quad (13)$$

<sup>1</sup>Analytical expression is given by the sum of the functions *arctan* and *ln*.

<sup>2</sup>This value is also included in the coefficient at the *arctan* in the solution of Eq. (11).

The average current during the transition between both the logiclevels is the coinciding DC power divided by the power supplyvoltage:

$$I_{av} = \frac{P_{DC}}{V_1 - V_2}. (14)$$

# ISO 9001:2008 Certified

# International Journal of Engineering and Innovative Technology (IJEIT) Volume 5, Issue 11, May 2016

#### IV. STATIC POWER MINIMIZATION

Static power dissipation dependence on the dimensions ofboth transistors  $M_1$  and  $M_2$  is discussed in this section. Staticpower is reduced by reducing an inverter's peak current (Fig.2)  $I_{max} = f(V_{SP})$ . Implying that, the switching point shouldbe closed to voltage  $V_2+V_{THN}$ (lower limit) or  $V_1-V_{THP}$ (upper limit) to turn off one of either transistor (equation 13). However, this state cannot really be obtained because  $R \rightarrow 0$  for the lower limit or  $R \rightarrow \infty$  for the upper limit (Fig. 3), as it is shown in Fig. 3. The setting of the optimal ratio Rto effective reduction of static power can be found by thesenstivity analysis of the switching point to the parameter R(Eq. 10). The sensitivity is defined as

$$C = \frac{dV_{SP}}{dR} \frac{R}{V_{SP}} = -\frac{1}{2} \frac{aR \left(V_1 - |V_{THP}| - V_2 - V_{THN}\right)}{\left(\sqrt{\frac{aR}{b}} + 1\right)\sqrt{\frac{aR}{b}} b}.$$

$$\frac{1}{\sqrt{\frac{aR}{b}} \left(V_2 + V_{THN}\right) + V_1 - |V_{THP}|}$$

(15)

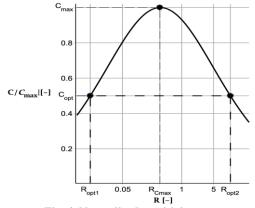

and decrease of the maximum sensitivity to the desired value sexpressed by parameter  $\delta$ :

$$\delta = \frac{C_{opt}}{C_{max}}. (16)$$

The  $\delta$  parameter will be determined by the simulations results as it is shown bellow.  $\delta$  is usually put to 0.5 because the voltage  $V_{SP}$  depends on the square root of R. Maximum sensitivity(in absolute value) given by the condition  $\frac{dC}{dR} = 0$  is at the point

$$R_{Cmax}|_{C=C_{max}} = \frac{V_1 - |V_{THP}|}{\frac{a}{b}(V_2 + V_{THN})}.$$

(17)

The normalized sensitivity curve to the maximum absolute value is shown in Fig. 4.

Finally, the optimal parameter R is derived from equations(15), (16) and (17),

$$R_{opt} = \frac{1}{16} \left[ \frac{2C_{max}\delta (V_{1a} + V_{2a}) + V_{12}}{\sqrt{\frac{a}{b}}C_{max}\delta V_{2a}} \pm \frac{\sqrt{V_{12}}\sqrt{4C_{max}\delta (V_{1a} + V_{2a} + C_{max}V_{12}\delta) + V_{12}}}{\sqrt{\frac{a}{b}}C_{max}\delta V_{2a}} \right]^{2},$$

(18)

Fig. 4. Normalized sensitivity curve

where  $V_{1a} = V_{1}$ -  $|V_{THP}|$ ,  $V_{2a} = V_{2} + V_{THN}$  and  $V_{12} = V_{1a}$ - $V_{2a}$ . Two solutions for the equation (18) exists. The first: $R_{opt1}$  for  $\frac{W_{n}}{L_{n}} \gg \frac{W_{p}}{L_{p}}$  and the second:  $R_{opt2}$  for  $\frac{W_{p}}{L_{p}} \gg \frac{W_{n}}{L_{n}}$  (Fig. 3). The calculated ratio R dependence on the chosenparameter  $\delta$  is shown in Tab. II.

#### V. SIMULATION RESULTS

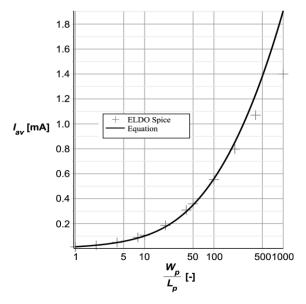

The DC parameters of the CMOS inverter were simulated by ELDO. The simulation circuit parameters are shown in Tab. I. The dependence of the average cross current (Eq. 14) on the width of the PMOS  $(W_p)$  or NMOS  $(W_n)$  transistorwas analyzed at the fixed channel lengths  $L_n$ ,  $L_p$ . These were determined based on the condition (1), respecting the value of the bis voltages, as it is shown in Table I.

TABLE I: SIMULATION CIRCUIT PARAMETERS

|                         | Parameter   | Value                                |

|-------------------------|-------------|--------------------------------------|

| Power supply            | $V_1$       | 4 V                                  |

| voltages                | $V_2$       | 2 V                                  |

| Threshold voltage       | $V_{THN}$   | 0.356 V                              |

| of the N/PMOS           | $ V_{THP} $ | 0.33 V                               |

| Coefficients calculated | a           | $3.43 \cdot 10^{-4}  \text{AV}^{-2}$ |

| from Eq.10              | b           | $7.45 \cdot 10^{-5}  \text{AV}^{-2}$ |

Analysis results in Tab. II show that an effective reduction of  $I_{av}$  is achieved when  $R \gg R_{Cmax}$  (solution  $R_{optl}$  of Eq. 18), consequently  $W_n \gg W_p$  and  $V_{SP}$  approach the lower limit, $V_{SP} \rightarrow V_2 + V_{THN}$ . This is physically caused by a greatermobility of electrons in the NMOS structure compared to themobility of holes in the NMOS dimensions. Otherwise, when  $R \ll R_{Cmax}$ , a very large disproportion between sizes of bothtransistors adversaly affects other properties of the inverter(transistors area, dynamic properties,...), as is shown bellow. Of course, the mean value of the cross current is not only a function of R, but depends on the specific value of  $W_n/L_n$ ,  $W_p/L_p$  respectively, as is shown in Fig. 5. The specific sizes of the NMOS and PMOS transistors can be setby additional application requirements (time delay, switchingcharacteristics), but the ratio R must be retained. Experience says that the optimal value of the parameter  $\delta$  is  $0.4 \div 0.6(Eq.\ 16)$  for practical design. Values of the ratio R and theaverage cross current  $I_{av}$  for this range of the  $\delta$  parameter are bold in Tab. II.

TABLE II: SIMULATION RESULTS

| Channel length of the N/PMOS: $L_p = L_n = 1 \mu m$ |                           |                          |                          |       |  |  |

|-----------------------------------------------------|---------------------------|--------------------------|--------------------------|-------|--|--|

| Width of the N/PMOS:                                |                           | $W_n = 40  \mu \text{m}$ | $W_p = 40  \mu \text{m}$ |       |  |  |

| δ                                                   | $R_{\mathrm{opt1,2}}$ [-] | $\mathbf{V_{SP}}[V]$     | I <sub>av</sub> [mA]     |       |  |  |

| 0.51                                                | 0.01                      | 3.47                     | 1.92                     | 0.018 |  |  |

| 0.63                                                | 0.02                      | 3.4                      | 1.69                     | 0.031 |  |  |

| 0.92                                                | 0.1                       | 3.16                     | 1.07                     | 0.106 |  |  |

| 0.985                                               | 0.2                       | 3.047                    | 0.798                    | 0.159 |  |  |

| 1                                                   | 0.34                      | 2.76                     | 0.309                    | 0.309 |  |  |

| 0.83                                                | 2                         | 2.67                     | 0.186                    | 0.372 |  |  |

| 0.7                                                 | 4                         | 2.59                     | 0.107                    | 0.430 |  |  |

| 0.66                                                | 5                         | 2.57                     | 0.089                    | 0.447 |  |  |

| 0.5                                                 | 11.7                      | 2.5                      | 0.047                    | 0.507 |  |  |

| 0.41                                                | 20                        | 2.46                     | 0.026                    | 0.541 |  |  |

| 0.31                                                | 40                        | 2.42                     | 0.013                    | 0.582 |  |  |

However, the optimal setting of R may not be optimal for the design of an inverter operating in digital circuits, where

## ISO 9001:2008 Certified

# International Journal of Engineering and Innovative Technology (IJEIT) Volume 5, Issue 11, May 2016

the switching point (Eq. 10) should be closed to the ideal value of half of the supply voltage. Therefore

$$R|_{V_{SP}=V_{DD}/2} = \frac{b}{a} \left[ \frac{V_1 - V_2 - 2|V_{THP}(V_{BS})|}{V_1 - V_2 - 2V_{THN}(V_{SB})} \right]^2$$

(19)

and corresponding sensitivity is about 0.98 and simulated  $I_{av}$ value is about ten times higher compared to the optimization process. The width of the PMOS transistor is sized to  $2 \div 3$ the width of the PMOS [1] transistor (lengths are the same), provided that  $V_{THN} \approx |V_{THP}|$ . This condition can not be satisfied in voltage convertors due to a different supply voltage  $V_I$ ,  $V_2$  in each of the convertor's stages and the different threshold voltage of each of the transistors (body effect, [1]–[5]).

Fig. 5. Cross current vs. the  $W_p/L_p$  ratio

# VI. CONCLUSION

The inverter draft for charge pump applications as an analogblock is discussed in this paper. Design process via *the symbolic description* is based on the low cross current (Eq. 8)during the transition between logic high and logic low levels. The sensitivity analysis of the switching point to the sizing of the transistors (Fig. 4) shows that it is possible to find the optimal ratio  $R = \frac{W_h}{L_n} \frac{L_p}{W_p}$ , while keeping a relatively big

ratioW/L value of each of the NMOS and PMOS transistors. It isvery favorable from a time response perspective. The formulaederived in this paper are applicable to the other MOSFETmodels including the parameters for the specified technologyprocess. Important implications of the optimization processcan be summarized in the following items:

• Asymmetric DC characteristics; switching point is notequal to the half supply voltage. It is not an appropriate configuration in a digital circuit (rise time versus fall time, noise margine for high versus low logic level,...), while these properties are not meaningful in analog ciruits. This fact has not been solved yet.

- Propagation delays between logic levels should be shortbecause of the possibility of setting small effectives witching resistances (large width) of the NMOS and PMOS. Propagation delays are not the same.

- The cross current is very small if the operating point of the inverter is set to the linear region of the voltagetransfer characteristics in comparison with cross current of the "symetrical" inverter of the same area.

- Static and dynamic properties are insensitive to the dimensionaltolerance of the transistors. The sensitivity of the proposed inverter switching point to the transistorssizing is always less than sensitivity of the inverter fordigital circuit applications. It follows from the principle of the design process.

All proposals were validated by the real circuit simulations.

Charge pumps are systems that are usually designed via the simulation because of its properties taken from both digital and analog circuits (Discrete-time analog circuits). Testing andmany iterations mean long-time simulation process. Thus, the analytical results will be very useful for the prediction of the required static and dynamic properties of these circuits (output voltage, rise time, etc.) without optimization process.

#### **ACKNOWLEDGMENT**

This work has been supported by the grant No. SGS14/191/OHK3/3T/13 of the CTU in Prague.

# REFERENCES

- [1] R. Baker, CMOS: circuit design, layout, and simulation. 3rd ed. Hoboken, NJ: Wiley, 2010, xxxiii, ISBN 9780470881323.

- [2] C. Hu, A. M. Nikenjad, W. Yang, D. Lu, BSIM4.6.4 MOSFET Model: User's Manual. UC Berkeley, 2009.

- [3] D. Stefanović, M. Kayl, Structured analog CMOS design. Dordrecht:Springer, 2008. ISBN 9781402085727.

- [4] C. Jager, Richard C.Travis N, Microelectronic circuit design. 3rd ed.Boston: Mcgraw-Hill, 2008. ISBN 9780073309484.

- [5] Y. Tsividis, C. McAndrew, Operation and modeling of the MOS transistor.3rd ed. New York: Oxford University Press, 2011, xxiv, 723 p.ISBN 0195170156.

- [6] Z. Hui, H. Mengshu, Z. Yimeng, T. Yoshihara, A 4-phase cross-coupledcharge pump with charge sharing clock scheme. Electronic Devices, Systems and Applications (ICEDSA), 2011, p. 73-76.

- [7] F. Pan and T. Samaddar, Charge pump circuit design. McGraw-Hill,c2006, xv, 247 p. ISBN 978-007-1470-452.

- [8] M.- S. Shiau, Z.-H. Hsieh, C.- C. Hsieh, H.-Y. Liu, D.-G. Liu, A NovelStatic CTS Charge Pump with Voltage Level Controller for DC-DCConverters. 2007 IEEE Conference on Electron Devices and Solid-StateCircuits. IEEE, 2007, p. 481-484.

- [9] L. Bisdounis, S. Nikolaidis, O. Loufopavlou, Propagation delay andshort-circuit power dissipation modeling of the CMOS inverter. Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactionson, 1998, Vol. 45, Issue 3, p. 259–270.

- [10] B. J. Cheek, N. Stutzke, S. Kumar, J. Baker, A.J. Moll, W.B. Knowlton, Investigation of circuit-level oxide degradation and

#### 18811. 2211-3134

#### **ISO 9001:2008 Certified**

# International Journal of Engineering and Innovative Technology (IJEIT) Volume 5, Issue 11, May 2016

its effect on CMOSinverter operation and MOSFET characteristics. Reliability PhysicsSymposium Proceedings, 2004, p. 110-116.

tolow-power low-voltage techniques and novel design and verification methodsof data converters.

- [11] M. Hafed, M. Oulmane, N. C. Rumin, Delay and current estimation in aCMOS inverter with an RC load. Computer-Aided Design of IntegratedCircuits and Systems, 2001 IEEE Transactions on. Vol. 20, Issue 1,2001, p. 80-89.

- [12] B. G. Gawalwad, S.N. Sharma, Noise analysis of a CMOS inverterusing the Itô stochastic differential equation. 2012 IEEE InternationalConference on, 2012, p. 344-349.

- [13] F.S. Marranghello, A.I. Reis, R.P. Ribas, CMOS inverter delay modelbased on DC transfer curve for slow input, Quality Electronic Design(ISQED), 2013, p. 651-657.

- [14] K. Matsumoto, T. Hirose, Y. Osaki, N. Kuroki, M. Numa, Switchingvoltagedetection and compensation circuits for ultra-low-voltage CMOSinverters. Circuits and Systems. MWSCAS '09. 52nd IEEE InternationalMidwest Symposium on, 2009, p. 483-486.

- [15] A.S. Chakraborty, M. Chanda, C.K. Sarkar, Analysis of noise marginof CMOS inverter in sub-threshold regime. Engineering and Systems(SCES), 2013, p. 1-5.

- [16] P. Chaourani, I. Messaris, N. Fasarakis, M. Ntogramatzi, S. Goudos, S. Nikolaidis, An analytical model for the CMOS inverter. Power and Timing Modeling, Optimization and Simulation (PATMOS), 2014, p. 1-6.

- [17] A.A. Hamoui, N.C. Rumin, An analytical current, delay, and powermodel for the submicron CMOS inverter. Electronics, Circuits and Systems, 1999, p. 1547-1551.

- [18] X. Peng, P. Abshire, Stochastic Behavior of a CMOS Inverter. Electronics, Circuits and Systems, 2007, p. 94-97.

- [19] A. Ruangphanit, K. Kiddee, A. Poyai, Y. Wongprasert, S. Niemcharoen, R. Muanghlua, The effects of temperature and device demension of MOSFETs on the DC characteristics of CMOS inverter. Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), 2012, p. 1-4.

#### **AUTHOR BIOGRAPHY**

**Jan Marek** was born in Prague on April 8, 1990. He graduated from the Czech Technical University in Prague in 2014 and is currently studying towards Ph.D. at the Department of Circuit Theory. His research interests deal with the design of modern analog circuits, as well as their optimization.

Jiří Hospodka was born in 1967. He received his Master's and Ph.D. degreesfrom the Czech Technical University in Prague in 1991 and 1995, respectively. Since 2007 he has been working as associate professor at the Department of Circuit Theory at the same university. Research interests: circuit theory, analogue electronics, filter design, switched-capacitor, and switched-current circuits.

Ondřej Šubrt was born in Hradec Králové on February 24, 1977. Heworks as analog design engineer with ASICentrum Prague, a company of the Swatch Group. At present, he has also been appointed an Ass. Prof. At the Faculty of Electrical Engineering, CTU Prague. His research interests being analog and mixed-signal integrated circuits design with emphasis